## $\begin{array}{c} \mathrm{CS}\ 61\mathrm{C} \\ \mathrm{Spring}\ 2024 \end{array}$

### Yan, Yokota Final

| Solutions last upd<br>PRINT Your Name                  |                                            |                         | ıy 13t                 | ch, 20          | 24    |               |                |                 |             |                |                  |          |                                                                             |

|--------------------------------------------------------|--------------------------------------------|-------------------------|------------------------|-----------------|-------|---------------|----------------|-----------------|-------------|----------------|------------------|----------|-----------------------------------------------------------------------------|

| Print Your Studen                                      | nt ID:                                     |                         |                        |                 |       |               |                |                 |             |                |                  |          |                                                                             |

| You have 170 minu                                      | utes. There a                              | re 10                   | ques                   | tions           | of va | aryin         | g cre          | dit a           | nd d        | liffic         | ılty (           | 100 poir | nts total).                                                                 |

|                                                        | Question:                                  | 1                       | 2                      | 3               | 4     | 5             | 6              | 7               | 8           | 9              | 10               | Total    |                                                                             |

|                                                        | Points:                                    | 12                      | 12                     | 13              | 10    | 13            | 10             | 9               | 8           | 13             | 0                | 100      |                                                                             |

| For questions with you may select on                   |                                            |                         | es,                    |                 |       |               | _              |                 |             |                | _                | re chec  | kboxes,<br>ices.                                                            |

| O Unselected                                           | option (comp                               | letely                  | y unf                  | illed)          |       |               |                | You             | can         | selec          | t                |          |                                                                             |

| <ul><li>Only one se</li></ul>                          | lected option                              | ı (con                  | nplet                  | ely fil         | lled) |               | <b>1</b>       | mult            | iple        | squa           | res              |          |                                                                             |

| O Don't do thi                                         | is (it will be a                           | grade                   | d as i                 | ncori           | rect) |               |                | (com            | plet        | ely fi         | lled)            |          |                                                                             |

| answers, your answinterpretation. For may not use more | wer is ambig<br>coding ques<br>blanks than | ious,<br>stions<br>prov | or th<br>with<br>ided. | e bub<br>ı blan | ble/c | heckl<br>ou m | oox is<br>ay w | s not<br>rite : | ent<br>at m | irely<br>ost o | filled<br>ne sta | in, we v | you write multiple vill grade the worst per blank and you ad of Oxdeadbeef) |

| •                                                      | , please incl                              | ide p                   | refixe                 | s in y          | our a | answ          | ers u          | nless           | oth         | erwi           |                  |          | and do not truncate                                                         |

| Write the statem                                       | ent below i                                | n the                   | e san                  | 1e ha           | ndw   | ritin         | g yo           | u w             | ill u       | se o           | n the            | rest of  | the exam.                                                                   |

| I have neither g if these answers                      |                                            |                         | _                      |                 |       |               | -              |                 |             |                | -                | •        | attempt to cheat;<br>CDEF points.                                           |

|                                                        |                                            |                         |                        |                 |       |               |                |                 |             |                |                  |          |                                                                             |

|                                                        |                                            |                         |                        |                 |       |               |                |                 |             |                |                  |          |                                                                             |

|                                                        |                                            |                         |                        |                 |       |               |                |                 |             |                |                  |          |                                                                             |

|                                                        |                                            |                         |                        |                 |       |               |                |                 |             |                |                  |          |                                                                             |

| Sign your name: _                                      |                                            |                         |                        |                 |       |               |                |                 |             |                |                  |          |                                                                             |

Clarifications made during the exam:

Q3.5: Assume CPU will always predict branches not taken.

Q8: All instances of uint32\_t and int should be int32\_t.

Q2: You may also use the registers x0, ra, and sp.

Q9: You may assume that all elements in matrices W and X are positive integers.

| O1 1 / | (1 noint) Con                     | wart tha <b>Q hit</b>       | uncionad hinary O                                 | 20001 1011 to dogim              | al, treating it as an unsigned                                                                      |

|--------|-----------------------------------|-----------------------------|---------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------|

| -      | integer.                          | vert the <b>6-bit</b>       | unsigned binary o                                 | 50001 1011 to decim              | ai, treating it as an unsigned                                                                      |

|        | Solution: 1                       | 1 + 2 + 8 + 16              | = 27                                              |                                  |                                                                                                     |

|        | (1 point) Con<br>represented, v   |                             | mal -510 to a <b>12-bi</b>                        | t two's complement l             | nexadecimal. If it cannot be                                                                        |

|        | Solution: -                       | -510 = 0b1110               | 0000 0010 = 0xE02                                 |                                  |                                                                                                     |

| 1<br>1 | floating point $1 \le  x  < 2$ as | number? Ex nd $y$ is a base | press your answer<br>-10 integer. For <b>Na</b> l | as $x \times 2^y$ , where $x$ is | s an IEEE-754 single precision<br>a base-10 number such tha<br>please leave the boxes blanl<br>ank. |

|        | $O + \infty$                      | O +0                        | O NaN                                             |                                  |                                                                                                     |

|        | O -∞                              | O -0                        |                                                   |                                  |                                                                                                     |

|        |                                   |                             | 10 0001 1100 =><br>• 0b1.1 = 1.5. $x = 1$         | _                                | at = 11000011 = 195 - 127 =                                                                         |

| -      | (0.5 points) A reading a file,    |                             |                                                   | erating system service           | , such as printing a string o                                                                       |

|        | • True                            |                             | O False                                           |                                  |                                                                                                     |

|        |                                   | System calls pystem service | •                                                 | ser-level processes to i         | nteract with the kernel or                                                                          |

| For Q  | Q1.5 – Q1.7 in                    | dicate the sta              | ge of CALL that                                   |                                  |                                                                                                     |

| Q1.5 ( | (0.5 points)                      | produces pse                | udoinstructions.                                  |                                  |                                                                                                     |

|        | Compile                           | er                          | O Assembler                                       | O Linker                         | O Loader                                                                                            |

| Q1.6 ( | (0.5 points)                      | produces mad                | chine code for the R                              | ISC-V instruction bne            | x0 x0 8.                                                                                            |

|        | O Compile                         | er                          | Assembler                                         | O Linker                         | O Loader                                                                                            |

|        | _                                 | =                           | chine code for the hat points to the da           |                                  | to magic_num, assuming                                                                              |

O Compiler

Linker

O Assembler

O Loader

Q1.8 (1.5 points) Suppose we have two 16-bit integer arrays, each with 73 elements, and we want to compute their element-wise product. If our RISC-V CPU has 128-bit registers and supports vmul, an instruction that performs 16-bit elementwise vector multiplication, what is the minimum number of mul and vmul instructions required to multiply these two vectors?

**Solution:** 128 / 16 = 8 numbers per addition. 73 elements / 8 numbers per addition = 9.125 additions. We need to do 9 vmul and 1 mul in total, which sums to 10.

Q1.9 (1.5 points) Suppose we have a program that takes 20 minutes to complete on a system with one core and takes 10 minutes to complete on a system with four cores. What fraction of this program is parallelizable? Express your answer as a simplified fraction.

Solution: Given Amdahl's Law  $e=\frac{1}{(1-f)+\frac{f}{s}},$  we know the terms s=4 and e=20/10. We need to solve for f.  $\frac{10}{20}=\frac{1}{(1-f)+\frac{f}{4}}$   $\Rightarrow \frac{10}{20}=(1-f)+\frac{f}{4}$   $\Rightarrow \frac{40}{20}=4(1-f)+f$   $\Rightarrow 2=4-4f+f$   $\Rightarrow -2=-3f$  So  $f=\frac{2}{3}$

Q1.10 (1.5 points) Given a cache with a hit rate of 80%, a hit time of 5 cycles, and a miss penalty of 20 cycles, what is the Average Memory Access Time (AMAT) for the system? Express your answer as an integer, rounding up if necessary.

```

Solution: 5 + (0.2 \cdot 20) = 5 + 4 = 9

```

For Q1.11 – Q1.14, choose which section of memory the value would live in. Assume this program compiles successfully.

```

1 int ada_mango(int adam) { return adam * adam; }

2 int main(int argc, char *argv[]) {

3   int *facade = malloc(sizeof(int) * 23);

4   char *brun = "lebrun";

5   return 0;

6 }

```

| Q1.11 (0.5 points) facade  |                        |                          |        |

|----------------------------|------------------------|--------------------------|--------|

| <ul><li>Stack</li></ul>    | <b>О</b> Неар          | O Static                 | O Code |

| Q1.12 (0.5 points) *facade |                        |                          |        |

| O Stack                    | <ul><li>Неар</li></ul> | O Static                 | O Code |

| Q1.13 (0.5 points) *brun   |                        |                          |        |

| O Stack                    | <b>О</b> Неар          | <ul><li>Static</li></ul> | O Code |

| Q1.14 (0.5 points) adam    |                        |                          |        |

| Stack                      | О Неар                 | Static                   | O Code |

Q2 61C16 (RISCV) (12 points)

A palindrome is a sequence of characters that reads the same backward and forward. For example, "civic" and "redder" are palindromes, but "wave" and "canal" are not palindromes.

Implement the RISC-V function find\_palindrome that takes as input a nonempty null-terminated string in a0 and its length (excluding the null-terminator) in a1. The function should return 1 in a0 if the string is a palindrome and 0 in a0 otherwise. Assume the input string contains only lowercase letters.

You may only use registers a0, a1, t5 and t6.

```

1 find_palindrome:

add a1 a0 a1 \mathbb{Q}_{2.1}

2

3 loop:

<u>addi a1 a1 -1</u>

4

5

1b t5 0(a0)

6

1b t6 0(a1)

Q2.4

7

bne t5 t6 not_palindrome

Q2.5

8

addi a0 a0 1

blt a0 a1 loop

9

Q2.7

10

addi a0 \times 01

11

jr ra

02.9

12 not_palindrome:

mv = a0 \times 0

13

14

jr ra

```

Q3 61Control Logic (13 points) Consider the standard 5-stage pipeline included in the CS 61C Reference Card. For each of the control logic signals below, indicate which stage the control signal would be used. Q3.1 (1 point) BrUn O IF OID EX O M O WB Q3.2 (1 point) RegWEn

O EX

O M

WB

WB

Q3.3 (1 point) MemRW O EX O IF OID O WB  $\mathbf{M}$ Q3.4 (1 point) WBSel O IF OID O EX O M

Q3.5 (3 points) Consider the following RISC-V code:

OID

O IF

```

1

addi t3 x0 8

2

addi t4 x0 6

3

lw t1 0(t3)

4

bne t3 t4 label

5

addi t3 t3 4

6 label:

7

addi x0 x0 0

```

Identify the first four hazards that occur when the above program is run on the standard 5stage pipeline included in the CS 61C Reference Card. Assume that the register file implements write-then-read (i.e. it allows reading out the data being written in the same cycle).

For each hazard, indicate the type of hazard and the line number(s) of the instruction(s) involved. If there are fewer than four hazards, select "None" for the unused rows.

| Hazard 1: | <ul><li>Structural</li><li>Data</li></ul> | <ul><li>Control</li><li>None</li></ul> | line 1 to 3 |

|-----------|-------------------------------------------|----------------------------------------|-------------|

| Hazard 2: | <ul><li>Structural</li><li>Data</li></ul> | O Control O None                       | line 2 to 4 |

| Hazard 3: | <ul><li>Structural</li><li>Data</li></ul> | <ul><li>Control</li><li>None</li></ul> | line 4      |

| Hazard 4: | <ul><li>Structural</li><li>Data</li></ul> | <ul><li>Control</li><li>None</li></ul> |             |

We can mitigate some hazards by adding a forwarding path from the ALU result directly back into the execute stage.

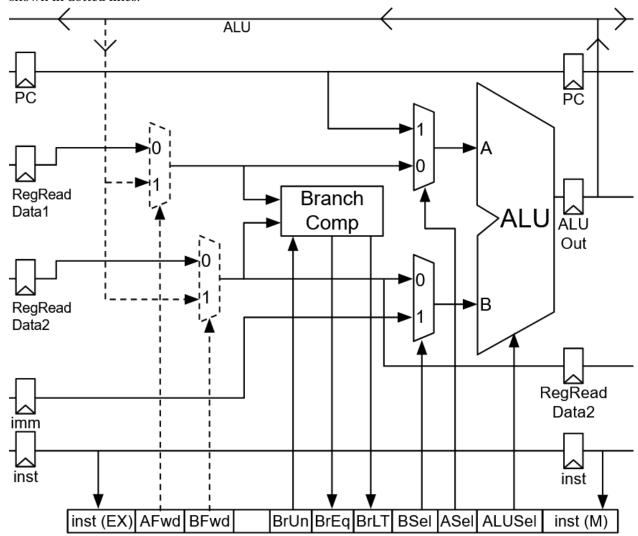

For Q3.6 – Q3.12 on the following page, assume we are working with the standard 5-stage pipeline included in the CS 61C Reference Card with the modifications shown below to implement this forwarding path. The diagram shows a subset of the datapath (specifically the EX stage), and modifications are shown in dotted lines.

| O Struct                             | ural                                                     | Data                               |                      | O Control                                                                                                 |       |

|--------------------------------------|----------------------------------------------------------|------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------|-------|

| signals determin<br>BFwd may be eith | e which, if any, forwardin<br>ner 0 or 1. Assume instruc | ng path should betion bits are zer | oe used.<br>o-indexe | ls: AFwd and BFwd. These con<br>If a stall is unavoidable, AFwd<br>ed.<br>y correctly describe AFwd and B | l and |

| instruction                          | nclusive) of the instruction                             |                                    | ero and e            | equal to bits <u>Q3.8</u> (inclusive) of                                                                  | f the |

| Q3.7 (0.5 points)                    | bits 15 to 19                                            |                                    |                      |                                                                                                           |       |

| Q3.8 (0.5 points)                    | bits 7 to 11                                             |                                    |                      |                                                                                                           |       |

| Q3.9 (1.5 points)                    | Select as few conditions a                               | s possible to ma                   | intain th            | ne correct behavior.                                                                                      |       |

| The in                               | struction in M writes to <b>r</b>                        | rd 🔳                               | The in               | struction in EX uses rs1                                                                                  |       |

| ■ The in                             | struction in M is not a loa                              | ad 🗆                               | The in               | struction in EX uses rs2                                                                                  |       |

| ☐ The in                             | struction in EX is not a st                              | tore                               | None o               | of the above                                                                                              |       |

| the instruct                         | •                                                        |                                    | nzero ano            | d equal to bits <u>Q3.11</u> (inclusive                                                                   | e) of |

| Q3.10 (0.5 points)                   | bits 20 to 24                                            |                                    |                      |                                                                                                           |       |

| Q3.11 (0.5 points)                   | bits 7 to 11                                             |                                    |                      |                                                                                                           |       |

| Q3.12 (1.5 points)                   | Select as few conditions a                               | s possible to ma                   | intain th            | ne correct behavior.                                                                                      |       |

| The in                               | struction in M writes to <b>r</b>                        | rd 🗆                               | The in               | struction in EX uses rs1                                                                                  |       |

| The in                               | struction in M is not a loa                              | ad                                 | The in               | struction in EX uses rs2                                                                                  |       |

| ☐ The in                             | struction in EX is not a st                              | tore                               | None o               | of the above                                                                                              |       |

Q3.6 (1 point) What type of hazard does this forwarding path attempt to mitigate?

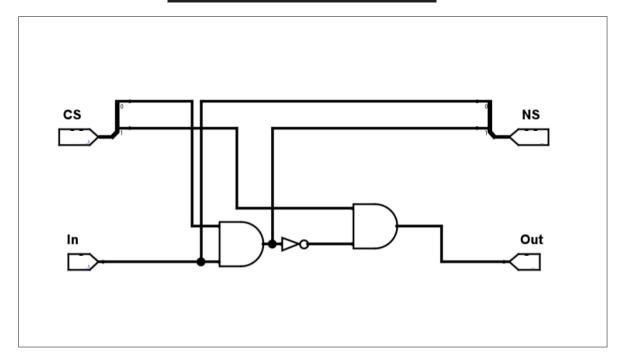

Q4 61CO (FSM) (10 points)

Q4.1 (4 points) We are designing an FSM for a carbon monoxide (CO) detector that receives input every half-second. A 0 indicates normal CO levels, and a 1 indicates dangerous levels. When at least two of the last three inputs are 1, the detector activates and outputs 1's indefinitely. When not yet activated, it outputs 0's. The FSM starts in state 00. Complete the transition table below to match this behavior, filling in the next state and output for each row. Some boxes are pre-filled for you.

For example, if the input to this FSM was 0b01 0010 1011 1000 1001,

the output should be 0b00 0000 1111 1111 1111.

- **CS** and **NS** represent the Current State and Next State of the FSM respectively

- **In** represents the input to the FSM (whether or not the CO level is dangerous)

- Out represents the output of the FSM (whether or not the detector is activated)

| CS | In | NS | Out |

|----|----|----|-----|

| 00 | 0  | 00 | 0   |

| 00 | 1  | 01 | 0   |

| 01 | 0  | 10 | 0   |

| 01 | 1  | 11 | 1   |

| 10 | 0  | 00 | 0   |

| 10 | 1  | 11 | 1   |

| 11 | 0  | 11 | 1   |

| 11 | 1  | 11 | 1   |

Q4.2 (2 points) We want to make our detector more sensitive. Now, the detector should output 1's indefinitely if **two of the last 12 samples** are 1's. What is the minimum number of states required to implement this updated detector as an FSM?

**Solution:** 13. One way to do this is to have a state per time step, e.g. "The last sample was 1 time step ago", all the way up to "The last sample was 11 time steps ago," as well as a state for "No samples detected," and "On." The key idea is that since we only care about 2 samples being detected, we can shortcut storing all possible configurations of the past 12 timesteps, since only the time steps that look like  $0 \cdots 010 \cdots 0$  are valid inputs that don't lock the FSM into the "On" state.

Q4.3 (4 points) A state transition table for a **different** FSM is shown below. Complete the circuit below to implement this FSM using only AND, OR, and NOT gates. Your implementation should minimize the critical path delay. Assume wires have negligible delay and each logic gate has the same delay.

| CS | In | NS | Out |

|----|----|----|-----|

| 00 | 0  | 00 | 0   |

| 00 | 1  | 01 | 0   |

| 01 | 0  | 00 | 0   |

| 01 | 1  | 11 | 0   |

| 10 | 0  | 00 | 1   |

| 10 | 1  | 01 | 1   |

| 11 | 0  | 00 | 1   |

| 11 | 1  | 11 | 0   |

Q5 61Caches (13 points)

Suppose our computer has 64KiB of memory and a 32B direct-mapped cache with 8B blocks.

Q5.1 (1.5 points) How many tag, index, and offset bits are in each address?

```

T: 11

```

**Solution:** 11 tag bits, 2 index bits, 3 offset bits

For Q5.2 – Q5.10, consider running the following program on our computer, assuming the cache starts off cold.

```

1 #define NUM_INTS 24

2 int32_t arr[NUM_INTS + 2]; // arr is located at address 0x2000

3 for (register int32_t i = 0; i < NUM_INTS; i += 1) {

4  arr[i + 2] = arr[i + 1] + arr[i]; // arr[i + 1] is accessed before arr[i]

5 }</pre>

```

Q5.2 (1 point) For each iteration of the for loop, how many memory accesses are there?

```

Solution: 3 (read arr[i+1], read arr[i], write to arr[i+2])

```

Q5.3 (1 point) For the **first** iteration of the **for** loop (i = 0), how many **hits** are there?

**Solution:** 1 hit. Accessing arr[i+1] results in a compulsory miss. The corresponding block (data stored at addresses with the same tag + index) has index = 0 and is loaded into the cache. The block contains 8 bytes of data corresponding to the 4 byte integers stored at &arr[i] and &arr[i+1]. Thus, accessing arr[i] results in a hit. Address &arr[i+2] has a different index (increased by 1, index = 1) and the access results in a compulsory miss.

| Q5.4 | (1.5 points) | Which of the          | e following | iterations | would ha | ve the | same | number | of hits | as th | ie <b>first</b> |

|------|--------------|-----------------------|-------------|------------|----------|--------|------|--------|---------|-------|-----------------|

|      | iteration of | the ${\tt for}\ loop$ | (i = 0)?    |            |          |        |      |        |         |       |                 |

$\square$  i = 3

$\square$  i = 6

$\square$  i = 22

$\square$  i = 4

$\square$  i = 7

$\square$  i = 23

$\square$  i = 5

$\square$  i = 21

None of the above

**Solution:** None of the above

arr[0] and arr[1] belong to the same block, arr[2] and arr[3] belong to the same block... For odd iterations (i = 1, 3, 5...), the block arr[i] belongs to and the block arr[i+1] and arr[i+2] belong to are already in the cache due to the previous iteration(s). The hit rate is 3/3. For positive, even iterations (i = 2, 4, 6...), the block arr[i] and arr[i+1] belong to are already in the cache. The block arr[i+2] belongs to is not initially in the cache (resulting in a compulsory miss). Therefore, the hit rate is 2/3. Only iteration i = 0 has hit rate = 1/3.

Q5.5 (1 point) For the **second** iteration of the **for** loop (i = 1), how many **hits** are there?

**Solution:** 3

Q5.6 (1.5 points) Which of the following iterations would have the same number of hits as the **second** iteration of the **for** loop (i = 1)?

$$i = 3$$

$$\square$$

i = 6

$$\square$$

i = 22

$$\square$$

i = 4

$$i = 7$$

$$\blacksquare$$

i = 23

$$\blacksquare$$

i = 5

$$i = 21$$

**Solution:** Odd iterations

Q5.7 (2.5 points) Considering all memory accesses for this program, how many compulsory misses, non-compulsory misses, and hits are there?

**Solution:** 13 compulsory misses, 0 non-compulsory misses. 24\*3 memory accesses - 13 misses = 59 total hits. Every miss that occurs is compulsory. Each block that is accessed and not currently in the cache has never been loaded into the cache before. 2 misses occur when i = 0. 0 misses occur when i is odd. 1 miss occurs when i is positive and even.

The program on the previous page has been copied below for your convenience:

```

1 #define NUM_INTS 24

2 int32_t arr[NUM_INTS + 2]; // arr is located at address 0x2000

3 for (register int32_t i = 0; i < NUM_INTS; i += 1) {</pre>

4 arr[i + 2] = arr[i + 1] + arr[i]; // arr[i + 1] is accessed before arr[i]

5 }

```

|       | Q5.8 – Q5.10, assume each subpa<br>ect-mapped cache with 8B block          | •                                      | er, our original cache is a 32B       |

|-------|----------------------------------------------------------------------------|----------------------------------------|---------------------------------------|

| Q5.8  | (1 point) If we change our origin rate for this program                    | al cache to a <b>24B</b> direct-mapped | cache with 8B blocks, the hit         |

|       | O increases.                                                               | remains the same.                      | O decreases.                          |

| Q5.9  | (1 point) If we change our originarate for this program                    | al cache to a 32B direct-mapped        | cache with <b>16B</b> blocks, the hit |

|       | increases.                                                                 | O remains the same.                    | O decreases.                          |

| Q5.10 | (1 point) If we change our original <b>LRU replacement policy</b> , the hi | •                                      | ve cache with 8B blocks and a         |

|       | O increases.                                                               | • remains the same.                    | O decreases.                          |

|       |                                                                            |                                        |                                       |

(10 points)

For Q6.1 to Q6.3, suppose we have a 4GiB virtual memory space, a 64KiB physical memory space, 128B pages, and a 4-entry fully associative TLB with a most-recently used (MRU) replacement policy.

Q6.1 (2.5 points) How many bits are in the offset, virtual page number (VPN), and physical page number (PPN)?

```

Solution: 7 offset bits. 32 total virtual address bits - 7 offset bits = 25 VPN bits. 16 total physical address bits - 7 offset bits = 9 PPN bits

```

Q6.2 (1.5 points) How many entries are in the page table? Write your answer as a power of 2 (e.g.  $2^5$ ).

```

Solution: 2^{25}

```

Q6.3 (1.5 points) Consider the following program executed by a particular process.

```

1 #define NUM_INTS 256

2 int32_t arr[NUM_INTS];

3 arr[0] = 0;

4 for (register int32_t i = 16; i < NUM_INTS; i += 16) {

5 arr[i] = i;

6 }</pre>

```

Suppose the address of arr is 0x1000 0000 and the execution of line 3 results in a TLB hit. When executing the for loop, what is the **minimum** number of TLB hits that may occur?

**Solution:** 8. Virtual addresses arr + 0 and arr + 16\*4\*1 have the same VPN, addresses arr + 16\*4\*2 and arr + 16\*4\*3 have the same VPN, ... In total, there are 256/16/2 unique VPNs accessed. Regardless of whether accessing a new VPN results in a TLB hit or miss (during iterations i = even multiples of 16), the corresponding entry of this VPN will be loaded into the TLB before the next iteration. As a result, a TLB hit must occur during iterations i = odd multiples of 16.

For Q6.4 – Q6.6, suppose we have a system as follows:

- 32-bit virtual addresses and 16-bit physical addresses

- 8-bit offsets

- One free physical page with PPN 0x49

- 4-entry fully associative TLB

The current state of the TLB and first 5 entries of the page table are shown below.

TLB Valid PPN **VPN** 1 0x00 00050x12 0 0x00 0001 0x18 1 0x00 0002 0x45 1 0x00 0003 0x78

# (first 5 entries) PTE 0xB256 0670 0xC490 8924 0x9845 6745

Page table

0x7256 0645

0xA158 9078

Each page table entry (PTE) is 4 bytes:

| 31    | 30             | 7   | 0   |

|-------|----------------|-----|-----|

| Valid | Other status b | its | PPN |

For each of the following virtual addresses, translate it into its corresponding physical address and determine what will happen during address translation. Assume each access occurs independently (not sequentially).

#### Q6.4 (1.5 points) 0x0000 01C9

**Solution:** VPN =  $0x00\ 0001$ . TLB valid bit =  $0 \rightarrow$  TLB miss. 2nd row of the page table: valid bit = 1 (page table hit) and PPN = 0x24. Physical address = 0x24C9.

- O TLB hit

- TLB miss and page table hit

- O Page fault

#### Q6.5 (1.5 points) 0x0000 0340

**Solution:** VPN =  $0x00\ 0003$ . TLB valid bit = 1 -> TLB hit. PPN = 0x78. Physical address = 0x7840.

- TLB hit

- **O** TLB miss and page table hit

- O Page fault

#### Q6.6 (1.5 points) 0x0000 0424

**Solution:** VPN =  $0x00\ 0004$  is not in the TLB -> TLB miss. 5th row of the page table: valid bit = 0 (page fault). VPN =  $0x00\ 0004$  is mapped to the free physical page with PPN = 0x49. Physical address = 0x4924.

- O TLB hit

- O TLB miss and page table hit

- Page fault

To estimate the value of  $\pi$  in C, we can generate random points within a unit square  $[0,1] \times [0,1]$ , count how many are within the unit circle, and use the following equation:

$$\pi \approx 4 \times \frac{\text{Points in Circle}}{\text{Total Points}}$$

A working implementation of estimate\_pi that uses exactly tot\_points points to estimate  $\pi$  is shown below. You may assume that random\_01 is a function that returns a number uniformly at random from the range [0,1) and can be called by multiple threads without changing its behavior. Note that a commented out OpenMP directive does nothing.

```

1 double estimate_pi(int tot_points) {

int points_inside = 0;

3

// #pragma omp parallel

4

{

5

// #pragma omp parallel for

6

for (int i = 0; i < tot_points; i++) {</pre>

7

double x = random_01();

double y = random_01();

8

if (x * x + y * y \le 1) \{ // Check if point is inside \}

9

10

// #pragma omp critical

11

points_inside++;

12

}

}

13

14

}

return 4 * ((double) points_inside / (double) tot_points);

15

16 }

```

For Q7.1 – Q7.4, select the below behavior that **best** describes the new behavior of the code if we include OpenMP directives by uncommenting the specified line(s). Each subpart is independent.

**Behavior A:** Incorrectly estimates  $\pi$ , or does not generate tot\_points points.

**Behavior B:** Correctly estimates  $\pi$  using tot\_points points faster than the original implementation.

**Behavior C:** Correctly estimates  $\pi$  using tot\_points points slower than the original implementation.

| <ul><li>Behavior A</li></ul>     | O Behavior B | O Behavior C |

|----------------------------------|--------------|--------------|

| Q7.2 (1 point) Uncomment line 5. |              |              |

| <ul><li>Behavior A</li></ul>     | O Behavior B | O Behavior C |

|                                  |              |              |

Q7.3 (1 point) Uncomment line 3 and line 10.

Q7.1 (1 point) Uncomment line 3.

```

O Behavior B

O Behavior C

Behavior A

Q7.4 (1 point) Uncomment line 5 and line 10.

```

```

O Behavior A

Behavior B

O Behavior C

```

Implement the function  $estimate_pi_fixed$  such that it correctly estimates  $\pi$  using  $exactly tot_points$  points, and is faster than the original  $estimate_pi$  above (i.e. without any lines commented out). If you do not need a blank, then leave it empty.

```

1 double estimate_pi_fixed(int tot_points) {

2

int points_inside = 0;

3

#pragma omp parallel

4

5

int local_points = 0;

6

int thread_num = omp_get_thread_num();

7

int num_threads = omp_get_num_threads();

8

for (int i = thread_num;

9

i < tot_points;</pre>

10

i += num_threads) {

Q7.7

11

double x = random_01();

12

double y = random_01();

13

if (x * x + y * y \le 1) {

14

// blank

Q7.8

15

local_points++;

Q7.9

16

}

17

}

18

#pragma omp critical

Q7.10

19

points_inside += local_points;

Q7.11

}

20

return 4 * ((double) points_inside / (double) tot_points);

21

22 }

```

Implement abs\_sum, a function that takes in a large array of integers arr of length arr\_size and calculates the sum of the absolute values of each element.

For example, the abs\_sum of the array [1, -2, -3, 4, 5, -6, 7, -8, 9] is 45.

For full credit, your implementation must run as fast as possible. You may assume **abs** is a function that correctly returns the absolute value of the argument.

- vector vec\_load(uint32\_t \*A): Loads 4 integers from memory address A into a vector

- vector vec\_store(vector \*mem\_addr, vector A): Stores vector A to mem\_addr

- vector vec\_setnum(uint32\_t num): Returns a vector where every element is equal to num

- vector vec\_and(vector A, vector B): Computes the bitwise AND between each pair of corresponding vector elements in A and B, and returns a new vector with the result

- vector vec\_or(vector A, vector B): Computes the bitwise OR between each pair of corresponding vector elements in A and B, and returns a new vector with the result

- vector vec\_xor(vector A, vector B): Computes the bitwise XOR between each pair of corresponding vector elements in A and B, and returns a new vector with the result

- vector vec\_sra(vector A, vector count): Shifts each pair of corresponding vector elements in A to the right by count with sign extension, and returns a new vector with the result

- vector vec\_add(vector A, vector B): Adds A and B together elementwise, and returns a

new vector with the result

- vector vec\_sub(vector A, vector B): Subtracts B from A elementwise, and returns a new vector with the result

```

1 int abs_sum(const int *arr, int arr_size) {

vector sum = vec_setnum(0);

3

vector shift = vec_setnum( 31 );

for (int i = 0; i < \frac{\text{arr_size} / 4 * 4}{\text{Q8.2}}; \frac{\text{i += 4}}{\text{Q8.3}}) {

4

5

vector vec = vec_load((vector *)(arr + i));

6

vector mask = vec_sra(vec, shift);

7

vec = vec_xor(vec, mask);

8

vec = vec_sub(vec, mask);

9

sum = vec_add(sum, vec);

08.5

10

}

11

int result[4];

12

vec_store((vector *)result, sum);

for (int i = /* Blank Q8.2 */; i < arr_size; i += 1) {

13

result[0] += abs(arr[i]);

14

15

return result[0] + result[1] + result[2] + result[3];

16

17 }

```

Note: This question was inspired by the game TIS-100, written by Zach Barth.

Multiprocess programming is great, but communication is so expensive... Taking inspiration from neural networks, we create new *micro-CPUs*, which work as follows:

- They have a reduced instruction set of RISC-V, where there are no load or store instructions.

Assume DMEM does not exist in our micro-CPUs because data memory accesses are "too slow".

- They also have built-in communication systems to "connect" (i.e. wire) each micro-CPU to up to four other micro-CPUs:

- For each of the four directions (up, down, left, and right), at most one micro-CPU is connected.

- All micro-CPUs share a clock but have separate IMEMs, PCs, and RegFiles.

- To communicate, two additional 32-bit RISC-V instructions are added:

- send rs1 direction starts a "send operation" to the micro-CPU in the specified direction. This operation will stall until the destination micro-CPU runs a corresponding recv. Once both sender and receiver are ready, sends the value in rs1 to the receiver.

- recv rd direction starts a "receive operation" from the micro-CPU in the specified direction. This operation will stall until the source micro-CPU runs a corresponding send. Once both sender and receiver are ready, saves the received value in rd.

Warmup: Suppose we connect two micro-CPUs that run programs A and B as follows:

#### **Micro-CPU Layout**

- In the layout above, each cell represents one micro-CPU, and adjacent cells represent a connection.

For example, the micro-CPU labeled A has right connected to the micro-CPU labeled B and left, up, and down connected to nothing.

- The label on each micro-CPU represents the program it will execute. For example, the micro-CPU labeled A will execute the program named **A**.

We would like to pass the value stored in the left micro-CPU's a0 register to the right micro-CPU's a0 register. If the value in a0 of the left CPU is 10, then the following pair of diagrams shows each micro-CPU's a0 registers before and after running their respective programs. A value of? indicates that it can be any value.

**Implement programs A and B** such that the micro-CPUs match the expected behavior described above. After each program is done, it should jump (or branch) to the label exit.

We now decide to implement parallel matrix multiplication by running seven programs, **A** through **G**, on micro-CPUs as follows:

- Input in a0 of the micro-CPUs

- Micro-CPUs labeled B contain elements of the matrix W.

- Micro-CPUs labeled D contain elements of the matrix X.

- Micro-CPUs labeled A and C contain the value

0.

- All other micro-CPUs may contain any value.

- Output in a0 of the micro-CPUs

- Micro-CPUs labeled E should contain elements of the output matrix.

- All other micro-CPUs may contain any value.

| Micro-CPU Layout |   |   |    |   |   |     |   |   |

|------------------|---|---|----|---|---|-----|---|---|

|                  |   |   |    |   | С |     | С |   |

|                  |   |   |    |   | D |     | D |   |

|                  |   |   |    |   | : | ٠.  | : |   |

|                  |   |   |    |   | D |     | D |   |

|                  | A | В |    | В | E | ••• | E | F |

|                  | : | : | ٠. | : | : | ٠.  | : | : |

|                  | A | В |    | В | E |     | E | F |

|                  |   |   |    |   | G |     | G |   |

For example, let's consider the following matrix multiplication operation along with the corresponding micro-CPU layout. The values in the a0 registers in each of the micro-CPUs before execution and the expected values after execution are also shown below.

#### **Example: Matrix Multiplication Operation**

$$\begin{bmatrix} \text{Matrix W} \\ 1 & 10 & 100 \\ 10 & 100 & 1 \\ 100 & 1 & 10 \\ 1 & 100 & 10 \end{bmatrix} \times \begin{bmatrix} \text{Matrix X} \\ 1 & 5 & 6 & 7 \\ 3 & 9 & 8 & 3 \\ 2 & 5 & 4 & 8 \end{bmatrix}$$

#### Output Matrix

$$= \begin{bmatrix} 231 & 595 & 486 & 837 \\ 312 & 955 & 864 & 378 \\ 123 & 559 & 648 & 783 \\ 321 & 955 & 846 & 387 \end{bmatrix}$$

#### **Example: Micro-CPU Layout**

|   |   |   |   | С | С | С | С |   |

|---|---|---|---|---|---|---|---|---|

|   |   |   |   | D | D | D | D |   |

|   |   |   |   | D | D | D | D |   |

|   |   |   |   | D | D | D | D |   |

| A | В | В | В | E | Е | E | E | F |

| A | В | В | В | E | Е | E | E | F |

| A | В | В | В | Е | Е | Е | Е | F |

| A | В | В | В | E | Е | E | E | F |

|   |   |   |   | G | G | G | G |   |

#### **Example:** a Before Program Execution

| -   |           |                 |                      |                                                |                                                                 |                                                                               |                                                                            |

|-----|-----------|-----------------|----------------------|------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|     |           |                 | 0                    | 0                                              | 0                                                               | 0                                                                             |                                                                            |

|     |           |                 | 1                    | 5                                              | 6                                                               | 7                                                                             |                                                                            |

|     |           |                 | 3                    | 9                                              | 8                                                               | 3                                                                             |                                                                            |

|     |           |                 | 2                    | 5                                              | 4                                                               | 8                                                                             |                                                                            |

| 1   | 10        | 100             | ?                    | ?                                              | ?                                                               | ?                                                                             | ?                                                                          |

| 10  | 100       | 1               | ?                    | ?                                              | ?                                                               | ?                                                                             | ?                                                                          |

| 100 | 1         | 10              | ?                    | ?                                              | ?                                                               | ?                                                                             | ?                                                                          |

| 1   | 100       | 10              | ?                    | ?                                              | ?                                                               | ?                                                                             | ?                                                                          |

|     |           |                 | ?                    | ?                                              | ?                                                               | ?                                                                             |                                                                            |

|     | 10<br>100 | 10 100<br>100 1 | 10 100 1<br>100 1 10 | 1 3 2 1 10 100 ? 10 100 1 ? 100 1 10 ? 1 100 ? | 1 5 3 9 2 5 1 10 100 ? ? 10 100 1 ? ? 100 1 10 ? ? 1 100 10 ? ? | 1 5 6 3 9 8 2 5 4 1 10 100 ? ? ? 10 100 1 ? ? ? 100 1 10 ? ? ? 1 100 10 ? ? ? | 1 5 6 7 3 9 8 3 2 5 4 8 1 10 100 ? ? ? ? 10 100 1 ? ? ? ? 100 1 10 ? ? ? ? |

#### **Example: a0 After Program Execution**

|   |   |   |   | ?   | ?   | ?   | ?   |   |

|---|---|---|---|-----|-----|-----|-----|---|

|   |   |   |   | ?   | ?   | ?   | ?   |   |

|   |   |   |   | ?   | ?   | ?   | ?   |   |

|   |   |   |   | ?   | ?   | ?   | ?   |   |

| ? | ? | ? | ? | 231 | 595 | 486 | 837 | ? |

| ? | ? | ? | ? | 312 | 955 | 864 | 378 | ? |

| ? | ? | ? | ? | 123 | 559 | 648 | 783 | ? |

| ? | ? | ? | ? | 321 | 955 | 846 | 387 | ? |

|   |   |   |   | ?   | ?   | ?   | ?   |   |

**Implement programs A through G** such that the micro-CPUs match the expected behavior described above and follows calling convention. After each program is done, it should jump (or branch) to the label exit.

```

A:

E:

send a0 right

mv a0 x0

Loop:

j exit

recv a1 left

B:

send a0 right

recv a2 up

Q9.3

Q9.12

beq a0 x0 exit

send a1 right

Q9.4

Q9.13

recv a0 left

mul <u>a3 a2 a1</u>

ј В

send a2 down

Q9.15

C:

send a0 down

beq a1 x0 exit

Q9.6

j exit

Q9.16

add a0 a0 a3

D:

Q9.17

send a0 down

j Loop

F:

beq a0 x0 exit

recv a0 left

Q9.8

recv a0 up

beq a0 x0 exit

Q9.9

Q9.19

j D

j F

Q9.10

Q9.20

G:

recv a0 up

Q9.21

beq a0 x0 exit

Q9.22

j G

Q9.23

```

#### Q10 61Colorless Epilogue

(0 points)

These questions will not be assigned credit; feel free to leave them blank.

Q10.1 The Coppersmith-Winograd algorithm to perform matrix multiplication has a time complexity of  $O(n^{2.3737})$ . What is the runtime of the matrix multiplication performed in Q9?

**Solution:** O(N)

Q10.3 If there's anything else you want us to know, or you feel like there was an ambiguity in the exam, please put it in the box below.

For ambiguities, you must qualify your answer and provide an answer for both interpretations. For example, "if the question is asking about A, then my answer is X, but if the question is asking about B, then my answer is Y". You will only receive credit if it is a genuine ambiguity and both of your answers are correct. We will only look at ambiguities if you request a regrade.

**Solution:** 「\\_('ツ)\_/「